- SYNPLIFY PRO NAME PRO

- SYNPLIFY PRO NAME SOFTWARE

- SYNPLIFY PRO NAME LICENSE

- SYNPLIFY PRO NAME WINDOWS

Set this option to enable/disable creation of this (NCF) file.

SYNPLIFY PRO NAME PRO

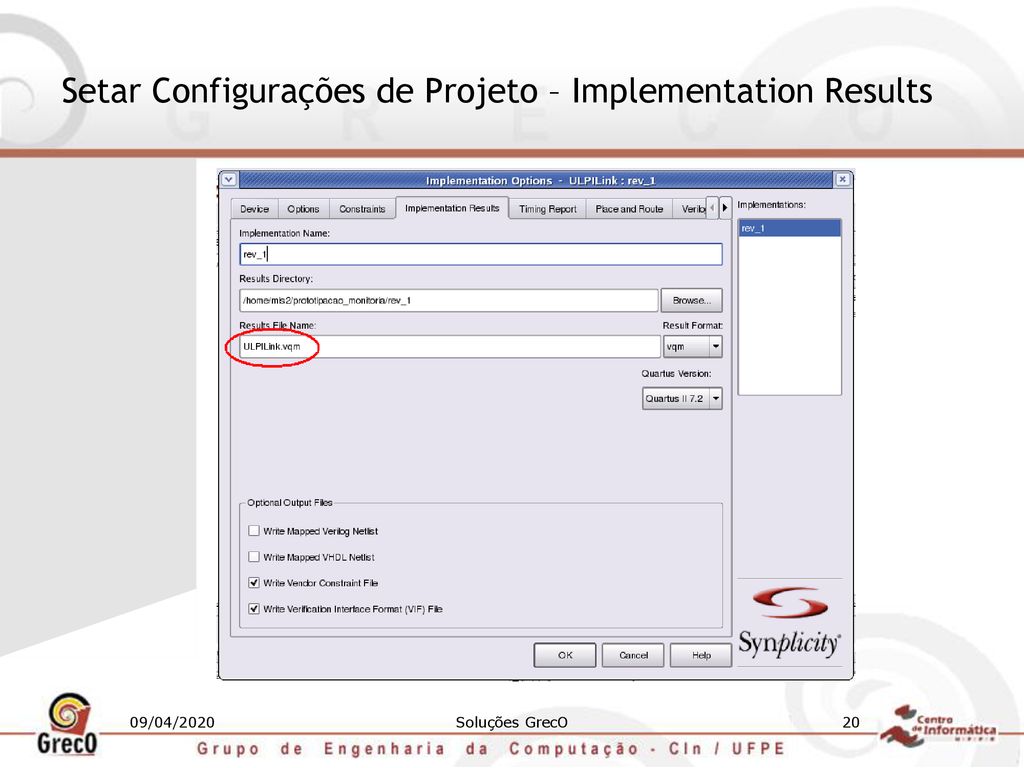

Synplify/Synplify Pro forward annotates user specified design constraints through a vendor constraint file. Write Vendor Constraint File - Default value is ON. Set this option to create a VHDL netlist for the mapped design.

Write Mapped VHDL Netlist - Default value is OFF. Set this option to create a verilog netlist for the mapped design. Write Mapped Verilog Netlist - Default value is OFF. Top Level Module This is the name of the top-level module being synthesized. Synplify allows you to display multiple implementations in the same Project view. You can synthesize again with another set of options to get another implementation. Implementation Name An implementation is one version of a project, run with a certain set of options.

SYNPLIFY PRO NAME SOFTWARE

The software will use the global clock frequency for timing-driven synthesis. For timing-driven synthesis, explicitly define the clock frequency. Frequency - Default value is 0 indicating area optimization. With this option checked, the software shares hardware resources like adders, multipliers, and counters wherever possible, and minimizes area. Check the resource sharing option when you set implementation options. The FSM Explorer uses the state machines extracted by the FSM Compiler when it explores different encoding styles. Unlike other synthesis tools that treat state machines as regular logic, the FSM Compiler extracts the state machines as symbolic graphs, and then optimizes them by re-encoding the state representations and generating a better logic optimization starting point for the state machines. The Symbolic FSM Compiler is an advanced state machine optimizer, which automatically recognizes state machines in your design and optimizes them. Set the desired synthesis, VHDL specific, Device and Constraint file options.ģ Following is a list of options: Synthesis Options Symbolic FSM compiler - Default value is ON. Select "Properties " to display synthesis options in the process properties dialog box. To set the options, right click on "Synthesize" in the process window of Project Navigator. Select your top-level design in the source window of project navigator. For complete description of these options, please refer to the design constraints section in the Synplify / Synplify Pro user guide or Synplify On Line Help.

Setting Synplify and Synplify Pro options Before you synthesize your design, you can set a variety of options for Synplify/Synplify Pro. Also choose the family and the device to be used for implementation in this option.Ģ B. Right click and choose "Properties " option to set Synplify/Synplify Pro as your synthesis tool. Select your project in the source window of project navigator. Create an ISE project using File->New menu button or open an existing ISE project. Setting Synplify/Synplify Pro as your synthesis tool 1. Following Xilinx device families are supported by Synplify and ISE package - Spartan, Spartan-II, SpartanXL, Virtex, Virtex-E, Virtex2, XC4000E, XC4000EX, XC4000L, XC4000XL, XC4000XLA A.

SYNPLIFY PRO NAME LICENSE

Also ISE needs Synplify to have a floating license in order to make use of Synplify s batch mode capability. ISE makes use of these values in the registry to invoke the latest version of Synplify.

SYNPLIFY PRO NAME WINDOWS

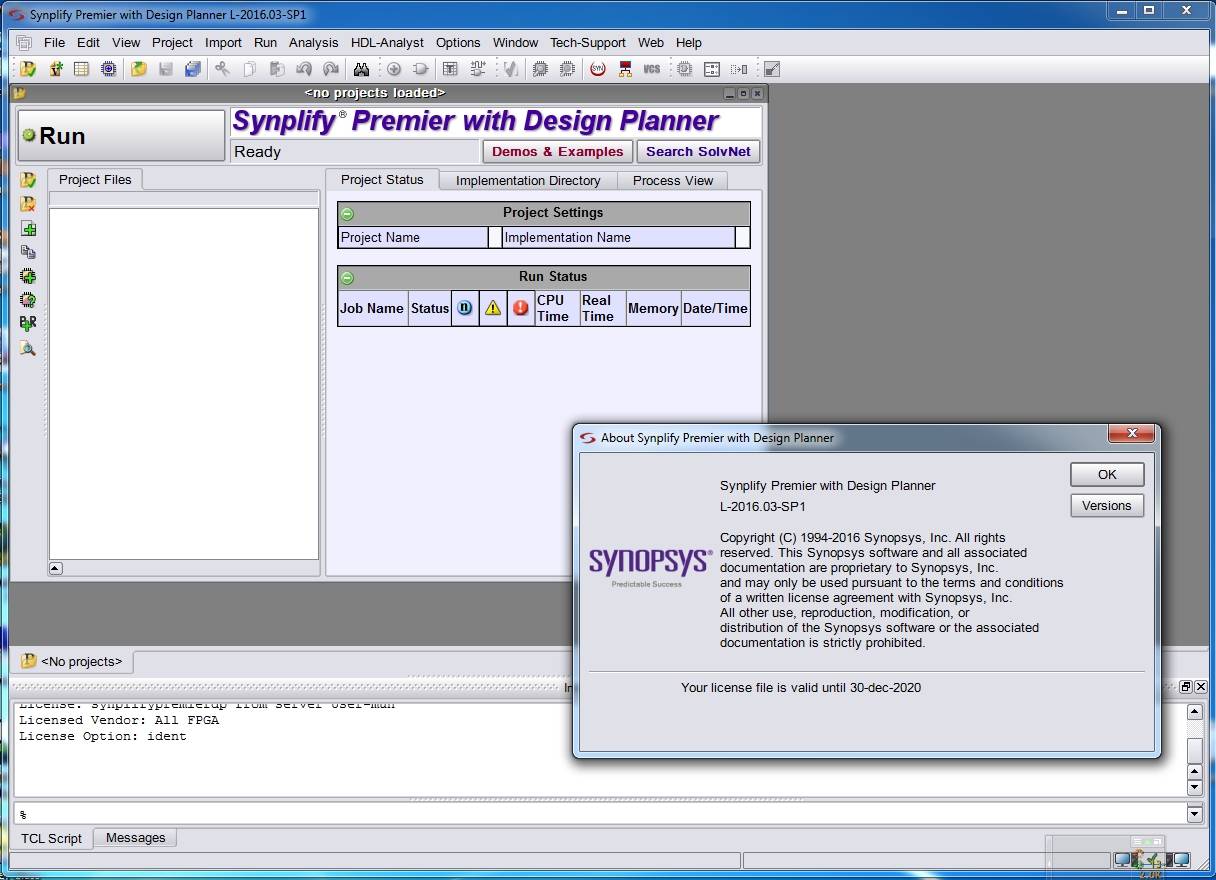

When Synplify is installed, it sets proper values in the windows registry. For detailed information about using Synplify tool to get best results, please refer to the Synplify and Synplify Pro user guide or Synplify On Line Help ISE works with Synplify / Synplify Pro 6.1 and onward. 1 Synplify and Synplify Pro synthesis and Options Synplify is a synthesis tool that can effectively synthesize VHDL, Verilog and Mixed language designs to create EDIF netlists.

0 kommentar(er)

0 kommentar(er)